300x250

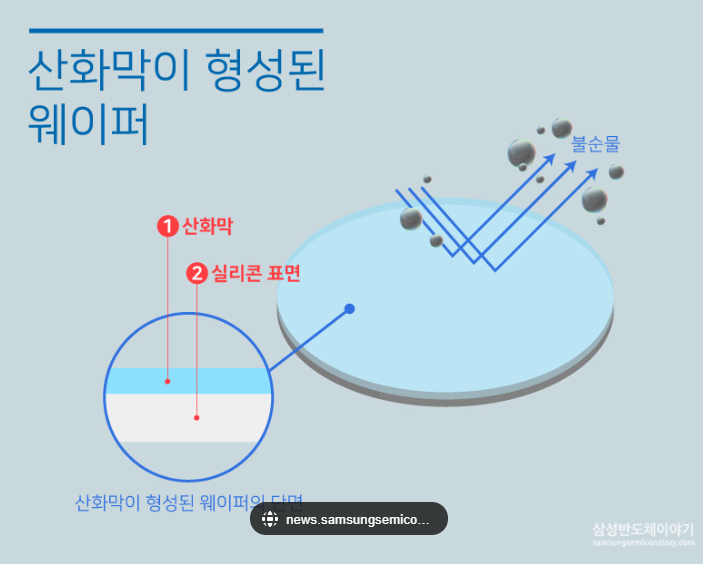

웨이퍼 준비

- 실리콘 웨이퍼 세척: 유기물, 금속 불순물, 파티클 등 제거

- 웨이퍼 표면 연마: 표면을 평탄하고 깨끗하게 연마

산화막 형성

- 열산화 공정: 웨이퍼를 고온의 산소 분위기에 노출시켜 얇은 게이트 산화막 성장

- 산화막 두께 조절: 메모리 소자 특성에 맞게 정밀하게 제어

폴리실리콘 증착

- 저압 화학 기상 증착(LPCVD): 실리콘 소스 가스를 이용해 게이트 전극용 폴리실리콘 증착

- 도핑: 원하는 전기적 특성을 위해 불순물 도핑 진행

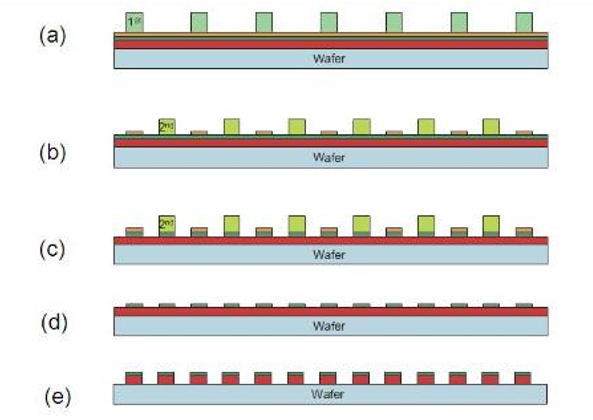

패터닝

- 포토리소그래피: 감광막 도포, 노광, 현상을 통해 셀 배열 패턴 형성

- 플라즈마 에칭: 패턴을 따라 폴리실리콘, 산화막 등 선택적으로 제거

- 증착, 노광, 식각으로 구성되며 각각 원하는 소재를 박막 형태로 깔고 노광으로 패턴을 인식한 후 필요하지 않은 부분을 제거하는 과정을 거친다.

소스/드레인 형성

- 이온 주입: 고에너지 이온빔을 이용해 소스, 드레인 영역에 불순물 주입

- 열처리: 활성화 및 확산 공정으로 소스, 드레인 영역 완성

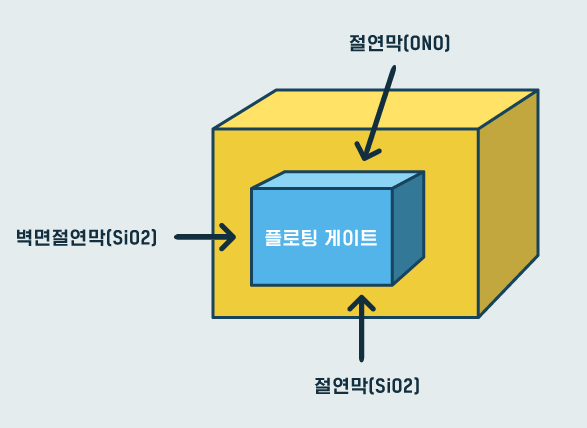

터널링 산화막 형성

- 열산화 공정: 부유 게이트 영역에 얇은 터널링 산화막 성장

- 산화막 두께 정밀 제어: 터널링 특성에 매우 중요

부유 게이트 형성

- 폴리실리콘 증착: 부유 게이트용 폴리실리콘 층 증착

- 패터닝: 포토리소그래피와 에칭으로 부유 게이트 패턴 형성

제어 게이트 형성

- 폴리실리콘 증착: 제어 게이트용 폴리실리콘 층 증착

- 패터닝: 포토리소그래피와 에칭으로 제어 게이트 패턴 형성

층간 절연막 형성

- ONO 구조 형성: 산화막-질화막-산화막 3중 층 증착

- 절연 특성 최적화: 부유 게이트-제어 게이트 간 전하 유지에 중요

금속 배선 형성

- 금속 증착: 소스, 드레인, 게이트 등에 금속(알루미늄, 구리 등) 배선 증착

- 패터닝: 배선 배치와 연결 최적화

패시베이션 및 검사

- 보호막 증착: 최종적으로 소자를 보호하는 패시베이션막 증착

- 전기적 특성 검사: 각 공정 단계별 전기적 성능 측정 및 분석

300x250

'주식 > 산업이야기' 카테고리의 다른 글

| 디스플레이 산업의 발전과 동향 (2023년~2024년) (0) | 2024.08.11 |

|---|---|

| 조선 섹터, 조선 기자재 밸류체인 (0) | 2024.07.28 |

| OIS란? OIS 액츄에이터, 손떨림 보정 기술 알아보기, 관련주는? (0) | 2024.07.26 |

| AESA란? 방위 산업 레이더 알아보기 (0) | 2024.07.24 |

| 반도체 8대 공정 간단하게 알아보기 (0) | 2024.07.16 |

댓글